오늘날 기술 노드(IC 포함)의 신뢰성을 개선하기 위해서는 전기적 조건과 열관리를 조정하는 것이 유일한 방법으로 보이기 때문에, OEM에게는 신뢰성 테스트가 매우 중요한 문제이다. DfR 솔루션(& 엑슬리트엣지)는 고객이 선택한 IC 부품의 신뢰성을 예측하기 위한 테스트 서비스와 모델을 제공한다.

테스트 기기나 측정 장비에는 처리하는 분석 데이터의 정확성을 보증하기 위해서 고 신뢰성, 고품질의 복잡한 IC가 탑재된다. 마이크로프로세서나 기타 복잡한 IC(예, FPGA)는 이들 기기 내에서 가장 중요한 부품으로 간주돼 왔다. 이런 부품들은 PCB 상의 다른 부품들처럼 전기적, 기계적, 열적 모드의 고장에 노출돼 있는데, 복잡하기도 하지만 회로 내에서의 중요한 역할로 인해 제 성능을 발휘하지 못하는 성능기반고장(performance-based failure)이 나오지 않도록 하는 것이 중요하다. 즉 이런 IC 소자의 파라미터 안정성은 시스템의 기능을 보증하기 위한 열쇠가 된다.

따라서 이러한 동작 파라미터(operational parameters)에 대한 수정은 그것이 설치돼 있는 시스템의 전체 수명에 직접적으로 영향을 미치고, 정해진 동작 기준을 증강(uprating)하거나 경감(derating)하는 기술적인 선택은 전반적인 신뢰성을 개선하거나 감소시킬 수 있다.

이들 IC에 대한 가속 테스트를 통해 성능과 신뢰성 간의 트레이드오프를 보다 확실히 이해할 수 있다. 지금도 끊임없이 계속되는 반도체 쉬링크(공정기술 미세화)는 전기적 회로를 안정적으로 사용하고 개발하는 측면에서 많은 도전과제를 제기한다. 회로가 더 작고 더 빨라지면 전류밀도는 더 높아지고, 전압 내성은 더 낮아지며, 전기장은 더 높아진다. 즉 IC는 이런 상황에서 초기 고장에 노출되어 수명이 짧아진다. 따라서 최신 기술이 적용된 전자장치와 회로에 이전에는 없던 새로운 고장 메커니즘이 발생하지 않도록 하는 것이 중요하며, 기존의 고장 유형도 더 나빠지지 않도록 보증해야 하기 때문에 지속적인 연구 활동과 방법이 요구된다.

지속적인 기술의 진보는 필연적으로 테스트 요구로 이어진다. 이 테스트를 통해 개별 고장 메커니즘과 새로 적용된 기술 사이의 일어날수 있는 모든 상호관계에 대해서도 새로운 모델을 만들어야 한다.

신뢰성 이슈에 대해 올바른 조치를 취하기 위해서 트랜지스터 아키텍처와 회로도를 재설계하려면 엄청난 시간과 예산이 든다. OEM 입장에서는 어떤 신뢰성 목표를 달성해야 하는지를 스스로 결정해야 한다. 또 이러한 목표를 부품 설계나 제조, 품질에 영향을 미치지 않고 달성할 수 있는지도 스스로 찾아야 한다. 이 경우 신뢰성 평가는 테스트를 통해 달성할 수 있다. 지금도 최신 기술 노드(IC 포함)의 신뢰성을 개선하기 위해서는 전기적 조건과 열관리 조정이 유일한 방법이므로, OEM의 입장에서는 테스트가 매우 중요한 문제가 됐다.

이러한 OEM의 요구를 충족시키기 위해, DfR 솔루션(및 엑슬리트엣지)는 고객들이 선택한 IC의 신뢰성을 예측하기 위한 테스트 서비스와 신뢰

성 모델을 제공한다.

접근법

산업계는 계속해서 무어의 법칙을 따르고 있다. 그러나 이러한 기술의 발전은 필연적으로 신뢰성 측정치의 부족으로 이어진다. 사람들은 프로세스만 올바르면 만들어진 제품도 신뢰성이 있을 것이라 오해하고, 테스트 기간 동안에는 단지 치명적 고장이 일어날 때까지의 시간만을 확인하기도 하고, 복잡한 디바이스의 경우 제품 단위 신뢰성 예측 평가 없이 그냥 넘어가기도 한다. 이런 신뢰성 과제에 대한 하나의 대안 방법론은 테스트용 디바이스(Device Under Test, DUT)를 하나의 블랙박스로 간주하는 것이다. 이는 어떤 온도에서 그 전기적인 파라미터를 모니터하고, 고유한 프로세스나 디자인 특성 정보가 없는 상태로 프로세스 기반 신뢰성 모델을 만드는 방법이다.

DfR 솔루션은 제조사 제품에 대한 광범위한 특성 분석을 하거나 고유한 설계 정보 접근이 없더라도 자체적으로 수행한 테스트 결과들로부터 신뢰성 모델을 만들어 제공할 수 있는 이런 블랙박스 접근법을 사용한다. 이 방법에서는 테스트 대상의 특성화를 위해 애플리케이션 개발 보드를 사용해 스트레스 반응을 측정한다. 이런 과정에서 테스트되는 디바이스의 열적, 전기적 반응이 시사하는 고장 메커니즘을 찾고 결정한다. 여기서 나온 결과를 기준으로 동작 허용오차(Operating margins)를 결정하고 가속 수명 테스트 파라미터를 설정한다.

이렇게 만들어진 테스트 결과는 IC 신뢰성 예측 계산기(Sherlock ICW)의 기초 자료로 사용되어, DfR 솔루션의 Sherlock ADA™ 내에 소프트웨어 모듈로 만들어져 제공된다.

부품 선택

새로 설계된 IC 제품에 대한 신뢰성 이슈나 관심이 있는 고객은 DfR 솔루션에 자사 제품의 신뢰성 테스트 서비스를 요청할 수 있다. 이 경우 DfR 솔루션은 여러 고객으로부터 요청받은 신뢰성 테스트 요청 목록에 포함시킨 후 일정을 잡아 테스트를 수행하고, 그 결과를 고객에게 제공한다. 여기서 신뢰성 결과는 Sherlock ICW에 반영된다.

만일 고객이 테스트 부품을 직접 제공하지 않더라도 원하는 테스트부품을 지정할 수 있다면, DfR 솔루션은 테스트 서비스를 수행할 수 있다.

만일 고객이 테스트 서비스를 받으려면, 동일한 12개 부품과 애플리케이션 보드를 제공해야 한다. 이 중 2개의 부품은 파괴적 특성화 프로세스 대상이 된다.

연결되지 않은 모든 개별 부품은 개발 보드와 함께 이미 조립된 상태로 만들어져 제공할 필요가 있다. 만약 고객이 원한다면, DfR 솔루션은 선택한 개발 보드와 부품을 찾아주는 서비스를 제공할 수도 있다.

테스트

DfR 솔루션은 선택된 부품들을 테스트하여 이것으로부터 시간 종속적 유전체 파괴(Time Dependent Dielectric Breakdown, TDDB), 음의 바이어스 온도 불안정성(Negative Bias Temperature Instability, NBTI), 핫 캐리어 주입(Hot Carrier Injection, HCI)에 대한 민감성을 평가한다. 필요한 테스트 방법을 올바르게 결정하기 위해, 그 부품을 열적으로나 전기적으로 먼저 특성화한다. 그리고 부품의 동작 범위를 결정하기 위해 단계적 스트레스를 적용해 테스트하고, 여기서 얻어진 동작범위는 최종적인 테스트 조건을 설정할 때 사용한다.

특성화

테스트용 디바이스(DUT)를 특성화하기 위해 애플리케이션 보드를 사용해 전기적 측정(electrical measurements)과 열적 이미지(thermal images)를 수집한다.

열 특성화

모든 IC는 전원이 인가되면 열이 발생한다. 허용된 최댓값 아래로 디바이스의 접합온도를 유지하려면, 반드시 IC로부터 패키지를 통해 주위(또는 회로 보드)로 열을 발산해야 하며, 그림 1에 나타낸 것처럼 냉각 판(Cold Plate)을 통해 열관리를 한다.

.jpg)

이 과정에서 부품들은 적외선(IR) 이미지를 얻기 위해 다이가 노출되도록 처리된다. 내부에 공간이 있는 부품의 경우, 디바이스 덮개를 제거하는 디리딩(delidding)이라고 불리는 과정을 포함하는데, 실링 또는 밀봉 용접 주위의 덮개를 연마함으로써 제거한다. 플라스틱 부품의 경우에는 봉합제 재료(encapsulant material)에 대한 화학적 기상 역 프로세스(chemical vapor deprocessing. Dissolving 또는 Decapsulation이라고도 부름)가 수행돼야 한다.

피막 제거 기법은 어떤 봉합제 재료인지, 사용된 프로세스가 어떤 것인지에 따라 크게 다르다. 몇몇 디바이스에 대해서는 이미 잘 알려져 있어서 쉽게 알 수 있지만, 재료구조가 복잡한 것들은 추가적인 조사가 필요하다. 재료를 특성화하는 기법은 디바이스 내에 트랜지스터 지오메트리를 확인하고 디바이스 패키징 요소를 평가하기 위해 사용될 수 있다.

디바이스의 열 반응을 확인하는 것은 특정한 기능을 처리하도록 구성된 다이 영역 내에서의 트랜지스터의 마이크로 환경이 어떠한지를 결정하기 위해 필요하다. 영역별 다이 위(on-die) 온도가 상승하면, 이는 다이 레이아웃의 한 특성이고 그 영역 신뢰성을 계산하는데 필요한 요소가 된다. 여기서 사용하는 방법론으로 JESD51 -온도 상승을 측정하는 가이드로서 부품 패키지의 열 측정에 대한 방법론(Methodology for the Thermal Measurement of Component Packages)- 이 있다.

이 프로세스는 테스트 후 망가지는 파괴적 테스트이다. 추가 디바이스가 필요하지만 다음과 같이 전기적 안정성 평가와 함께 동시에 수행될 수 있다.

.jpg)

전기적 안정성 평가(단계 스트레스 테스트)

부품은 그 동작 허용범위가 어떤지를 탐색하고 확인하기 위해서 단계 스트레스 테스트(Step Stress Test)를 받는다. 부품이 수많은 입력 값에 대해 퍼즈 테스트(Fuzz Test) 되는 동안 출력 반응이 규격 내에 있는지를 결정하기 위해 파라미터적 모니터링이라는 기법이 사용된다. 퍼즈 테스트는 디바이스에 내재된 잠재적인 비정상 거동(오류)을 알아내기 위해 디바이스에 상승된(Elevated), 비 유효한(Invalid), 예측 불가능하거나(Unexpected) 또는 임의 입력값들을 적용해 테스트하는 반자동 테스트 기법이다.

파라미터적 고장을 특성화하는데 있어서 어려운 점은 각 디바이스마다 고유한 차별적인 파라미터를 가지고 있으며, 이 파라미터 각각은 어떤 범위의 값들로 지정된다는 것이다. 하나의 제품군에 속한 대부분의 디바이스들은 공통된 경향이 있는 반면, 각 제품군은 고유한 특성을 지니고 있다. 예를 들어 증폭기와 아날로그-디지털 컨버터(ADC)는 모두 아날로그 디바이스이나 서로 다른 특정 파라미터를 가지고 있다.

허용범위 결정

부품은 작동하는 동안 최대 또는 최소 동작온도 범위에서 동작해야 한다. 이러한 동작 허용범위를 찾는 것은 챔버 내에서 DUT로부터 신호발생이 중단될 때까지 DUT의 온도를 직접 올리거나 내리는 단계를 택함으로써 정의할 수 있다. 동작 HALT 한계를 정의하는 프로세스에서처럼 온도 한계치는 각 테스트에 대하여 10 ℃ 안전계수(safety factor)를 추가해가면서 구한다.

최대 온도

데이터 로거가 실시간으로 다이 온도를 기록하는 데 사용되며, 부품의 파괴적 한계는 제한된 전력 소모(limited power dissipation)로 확인된다.

최소 온도

저온 측(cold side) 셋업은 액체 냉각 블록 내에 맞추기 위해 애플리케이션 보드에 가공 부품 및 수정 부품을 이용해서 구성한다. 그림 4는 만든 히트싱크 위에 실장된 평가 카드를 보여준다. 만일 필요하다면, 열전대를 히트싱크 스택업의 열적 부품에 붙이고, 평가 카드 후면(DUT 뒤)과 보조적 냉각 블록에도 배치하여 온도를 측정한다.

.jpg)

가속 수명 테스트

총 10개의 부품을 5개씩 고온 및 저온 조건에서 각각 테스트한다.

테스트 셋업

하나의 동일한 테스트 셋업 내에서 두 개의 독립적인 테스트가 이루어질 수 있도록 DUT 테스트 환경을 구성한다. 두 테스트 사이에는 테스트가 진행되는 동안 서로가 방해받지 않고 각 시스템으로부터의 헬스 모니터링 데이터(Health Monitoring Data)를 저장하기 위해 중재 컴퓨터를 배치한다. 이렇게 구성한 테스트 스키마는 DUT의 현상태와 역사적인 추세 데이터에 대한 실시간 접근을 동시에 허용한다. 그림 5는 이러한 셋업의 다이어그램 예이다.

.jpg)

애플리케이션 보드의 물리적 셋업의 경우, 두 개의 독립적인 환경을 구성해 만든다. 즉 HCI 테스트가 저온에서 실행되도록 셋업되는 동안, TDDB와 NBTI 테스트는 고온으로 실행하도록 셋업된다. 테스트의 고온 측(hot side)은 열적 이탈을 방지하기 위해서 팬을 제어한다. 테스트의 저온 측(cold side)은 DfR 솔루션이 자체 설계한 냉각기(Chiller) 셋업에 의해 제어된다. 그림 6은 두 테스트 타입의 이미지 예이다.

.jpg)

테스트 모니터링

전압, 주파수, 동작 스트레스 요소는 특별히 만들어진 번인(burnin) 및 벤치마킹 웨어(소프트웨어, 하드웨어, 펌웨어)를 통해 제어되고 수정된다. 초기 특성화가 DUT에 대한 전압, 주파수, 동작상태의 종합된 한계를 결정하기 위해 시행된다. 표 1은 그 예이다.

.jpg)

고온 및 저온 테스트는 일관성을 유지하기 위해 초기 특성화 과정에서 사용된 벤치마킹 웨어들을 사용해 모니터한다. 여기서 얻어지는 데이터는 매주 기록된다. 그림 7은 이 소프트웨어 벤치마크 도구 중 하나가 보여주는 스크린샷 샘플이다.

고장 확인 절차

심각한 기능적 고장(hard functional failure)은 전압, 온도, 주파수, 입력 타이밍 범위가 다르기 때문에 일관성 있게 발생하는 고장으로 정의된다. 이러한 것들은 진짜 고착된 결함(stuck-at faults) 때문에 발생하거나 디자인의 약점으로 인한 스트레싱 프로파일성(stressing profile) 손상을 초래하는 결점 때문에 발생하는 것이 일반적이다. 가벼운 기능 고장은 전압, 온도, 주파수 또는 타이밍에 따라 변할 수 있다. 가벼운 기능 고장은 타이밍이 정상적으로 스위칭되지 않는 내부 회로 노드에 의해 초래되는 것이 보통이다. 이 두 타입 고장이 평가의 핵심인데, 가벼운 기능 고장도 잠재적 고장 메커니즘에 대한 통찰을 제공할 수 있기 때문에 중요하다.

비록 DUT의 명확한 파괴 고장이 마모형 스트레스 테스트를 통해 알고자 하는 것이라 할지라도 시스템 내 특정 기능의 가벼운 파괴나 고장도 역시 고장까지 시간 데이터로 고려된다. 그림 8에 제공된 플로차트는 테스트 시 이상 거동이 관측될 때 취해야 하는 단계들을 감안해 구성한 것이다.

이 고장 모드 확인 플로차트는 테스트 플랫폼 상에 비정상적인 거동이 감지될 때마다 사용된다. 이러한 비정상적인 거동은 다음 같이 분류된다.

분석과 모델 생성

DfR 솔루션은 복수 고장 메커니즘 방법론1을 이용한 IC 신뢰성 계산기(IC reliability calculator)를 개발했다. 이 방법론을 통해 IC 소자의 복수 고장 메커니즘이 동시에 반영된 기능 저하 모델을 성공적으로 만들었다. 이 복수 메커니즘 모델은 각 관심 반도체 메커니즘에 대한 독립적인 가속계수들을 사용한다. 즉 시간 종속적 유전체 파괴(TDDB), 핫 캐리어 주입(HCI), 음의 바이어스 온도 불안정성(NBTI)을 디바이스 내의 트랜지스터 스트레스 상태에 기초하여 추론한 것이다.

IC 수명은 반도체 재료, 특성 크기, 고장 메커니즘 민감성, 그리고 디바이스에 존재하는 동작조건 상의 정보로부터 계산된다.

시간 종속적 유전체 파괴(TDDB)

TDDB는 전자 터널링 전류(electron tunneling current)로 인해 기판(substrate)으로 게이트 산화물을 통한 도선 경로(conducting path)가 형성되어 야기된다. 만일 터널링 전류가 충분하다면, 그것은 코로나 아크(corona arcing)와 유사하게 산화물과 주변 회로에 영구적인 손상을 초래한다. 이 손상은 성능 저하와 궁극적인 심한 파괴 고장으로 이어진다. 만일 이 터널링 전류가 매우 낮게 유지되면, 그것은 게이트를 켜기 위해 필요한 전기장을 증가시키고 그 기능성을 방해한다.

이 게이트 유전체는 비교적 낮은 전기장 때문에 큰 특성 요소 크기(> 5 nm 이상의 산화물 두께)를 가진 디바이스에 대해 오랜 기간에 걸쳐 파괴가 이루어진다. 특성 요소 크기가 작아짐에 따라 코어 전압은 줄었지만 공급 전압은 일정하게 유지된다; 따라서 로컬 전기장은 작은 노드에서 더 커진다. 이러한 전기장의 세기가 관심사인 이유는 높은 전기장이 TDDB의 효과를 악화시키기 때문이다.

인텔의 문서2는 산화물 두께 대비 NMOS와 PMOS TDDB에 대한 일관된 경향이 플래너(planar)와 트라이게이트(tri-gate) 트랜지스터 모두에서 발견되었고, 파괴를 통제하는 새로운 물리적 메커니즘이 트라이게이트 설계에 도입되지 않았다고 명시하고 있다. 인텔은 데이터를 업계 표준 열화학적 모델에 잘 맞출 수 있었다. 트라이게이트(FinFET) 타입 트랜지스터는 여러 파운드리의 24 nm 이하 기술 노드에서 흔히 볼 수 있다. 그 열화학적 모델은 전기장의 세기에 대한 파괴 수(breakdown times)의 상관관계를 잘 보여준다.

실리콘 분자의 구조와 결합은 영향을 받는다. TDDB는 Si-O 결합의 파괴를 초래하기 때문에, 이들로 산소 결핍(oxygen vacancies) 위치들을 생성한다. 산소 결핍을 가진 Si 분자에 대한 중요한 사실은 Si-Si 결합은 매우 약하고, Si-O 결합은 높은 극성이 있다는 것이다. 강한 전기장의 존재 하에서는 이들 분자의 극성이 변하여 Si-Si 결합의 파괴로 이어지는 수정 격자(crystal lattice)의 왜곡을 초래할 수 있다. 남아있는 전자는 가전자대(valence band)로 떨어져 홀트랩(hole trap)을 초래한다. 소프트 브레이크다운(soft breakdown, SBD)이 발생하는 동안, 트랜지스터는 ‘0’과 ‘1’ 사이의 스위칭 이슈를 갖게 될 것이다. 하지만 일반적으로 디지털 논리 단계들은 신호를 통제할 수 있다. 그림 9는 래치업으로 이어질 수 있는 타이밍 조건 전환을 보여준다.

.jpg)

열화학적 모델에서, TDDB의 원인은 실리콘-도핑 실리카 인터페이스(silicon-doped silica interface)에서 장-증강 열적 결합 파괴(field-enhanced thermal bond-breakage) 때문이다. 이 전기장은 열적 결합 파괴에 필요한 활성화 에너지를 줄임으로써 고장에 대한 반응속도를 기하급수적으로 증가시킨다. 따라서 고장까지 시간(Time to failure)은 기하급수적으로 줄어든다. 산화물의 전기장은 그 산화물 두께를 가로지르는 전압과 직접 관련이 있다. 그러므로 우리는 코어전압을 추적함으로써 가속 조건 하에서 고장까지 시간을 비교할 수있다. 이 열화학적 모델의 고장까지 시간 방정식은 다음과 같다.

![]()

여기서:

A0는 재료와 프로세스에 의존하는 임의 스케일 계수γ는 장 가속 파라미터(field acceleration parameter) Eox 유전체를 가로지르는 전기장 Vox는 유전체(게이트 전압 또는 코어 전압)에 인가된 전압 EA는 그 메커니즘의 활성화 에너지 k는 볼츠만 상수 T는 온도 조건

핫 캐리어 주입(HCI)

HCI는 드레인 바이어스 전압으로 스트레스를 받는 NMOS나 PMOS 디바이스 모두에서 발생한다. 높은 전기장은 캐리어(전자 또는 정공)을 활성화시켜, 캐리어가 게이트 산화물 영역으로 주입되어 더 약한 Si-H 결합을 파괴한다. 이는 캐리어가 채널을 따라 이동하여 디바이스의 드레인 끝 근방에서 충격 이온화를 경험하게 되면서 발생한다. 약화된 게이트 유전체와 벽 인터페이스(wall interfaces)는 스폰지처럼 되고 전자 또는 정공을 잡아, 임계전압(threshold voltage)을 변하게 하고, 이는 순차적으로 서브-임계누설전류(sub-threshold leakage current)의 전환으로 이어진다.

HCI는 바이어스 전압의 증가에 의해 가속화되고, 더 낮은 스트레스 온도에서 두드러진 메커니즘이다. 따라서 다른 고장 메커니즘과는 달리, 핫 캐리어 손상은 가속 수명 테스트에서 일반적으로 사용하는 HTOL(High Temperature Operating Life) 테스트에서 복제되지 않는다. HCI 기능 저하는 치명적인 고장보다는 회로 속도의 감소를 초래한다. 충분히 큰 속도 감소는 디바이스 고장과 시스템 불안정성의 원인이 될 수 있다.

인텔의 연구는 회로 속도가 트라이게이트 트랜지스터에 존재하는 핀 폭에 일부 의존성이 있다는 것을 보여준다. 핫 캐리어의 열화는 게이트의 각 측면 핀 위에 생성된 전기장 프로파일에 의해 악화될 수 있다. 전기장은 일반적으로 서로 다른 핀 폭에 대해 서로 다른 최적화 지점에 맞춘 도핑 수준과 접합 프로파일에 의해 추가적으로 조정된다. 이것들은 감소한 핀 폭과 함께 상승한 기능 저하를 보이는데, 이는 상대적으로 커진 종횡비(aspect ratio)를 가진 핀으로부터 흩어진 캐리어를 포획하기 위한 측벽(sidewall)의 증가된 확률 때문일 가능성이 높다. 트라이게이트(또는 FinFET) 스타일 트랜지스터는 여러 파운드리의 24 nm 이하 기술 노드에서 널리 사용된다.

HCI에 의해 야기된 기능 저하의 일반적인 모델은 아이어링(Eyring) 모델을 사용하여 설명될 수 있다. 양산 디바이스에서는 측정할 수 없는 기판 전류는 트라이게이트 트랜지스터3의 HCI 모델링에서 볼 수 있듯이 드레인 전압에 상관관계가 이어질 수 있다. 고장까지 시간 방정식을 보면:

.jpg)

여기서:

AB는 재료와 프로세스에 의존한 임의 스케일 계수(arbitrary scale factor) W/L는 채널의 유효 넓이와 길이의 비율 Vd는 MOSFET에 적용된 드레인 전압 N은 장-가속 파라미터 EA는 이 메커니즘의 활성화 에너지 k는 볼츠만 상수 T는 온도 조건

음의 바이어스 온도 불안정성

음의 바이어스 온도 불안정성(Negative Bias Temperature Instability, NBTI)은 음의 드레인 바이어스 하에 있는 PMOS 트랜지스터 기능을 저하시킨다. NBTI는 Si-H 결합을 파괴하고 트랜지스터내 실리콘-산화물 인터페이스에 위치한 Si-불포화 결합(Si-dangling bonds)의 패시베이션(passivation)을 유발하는데, 이는 그 임계전압을 증가시키는 원인이 된다. NBTI는 복구 프로세스를 가지고 있다는 점에서 다른 고장 메커니즘과는 구분된다. 이는 NBTI 복구 양이 기능저하의 양과 동일한 곳에서 기능 저하의 비율 축소를 야기할 수 있다.

또한, NBTI는 디바이스의 전기적 허용오차 범위 내에서만 디바이스의 기능을 저하시킬 수 있다. 이러한 메커니즘의 평가는 하나의 제조 공정이 더 작은 기술 노드로 축소되면서 민감해지는 지를 확정하기 위해 일반적으로 필요한 것으로 보인다.

CMOS 쌍이 토글될 때, NBTI는 이런 결합을 재패시베이팅(repassivating)에 의해 복구되도록 할 수 있다. 이 거동은 유전체 파괴로 발생하는 결함들의 축적과 유사하지만, 고장을 유발하는 파괴 이벤트라기보다는 하나의 파괴 이벤트가 복구로 이어지는 점에서 차이가 있다.

이런 프로세스가 FPGA 기술에서는 어느 정도 제어할 수 있는 반면, 정적 레이아웃을 가진 다른 디바이스는 이런 메커니즘을 완화할 수 없다.

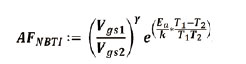

NBTI의 일반적인 Power-Law 모델은 다음과 같이 제공된다.

여기서:

아래 첨자 1은 사용조건을 위한 것 아래 첨자 2는 테스트 조건을 위한 것 Vgs는 MOSFET 상에 가해진 드레인 전압 감마(γ)는 전압 가속 파라미터 EA는 그 메커니즘의 활성화 에너지 k는 볼츠만 상수 T는 온도 조건

라이브러리 접근

고객들은 테스트된 부품의 라이브러리에 접근할 수 있다. 이 라이브러리에는 www.dfrsolutions.com/calculators/에 있는 온라인 계산기를 이용하는 것처럼, 자신의 ID와 패스워드를 이용해 접근한다. DfR 솔루션(& 엑슬리트엣지)는 이 IC 수명 예측 모델을 Sherlock Automated Design Analysis™ 소프트웨어 도구에 IC 마모 예측 모듈이라는 하나의 모듈로 상품화할 예정이다. 원하는 고객에 한하여 베타 버전을 사용해 볼 수 있다.

AEM_Automotive Electronics Magazine

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>