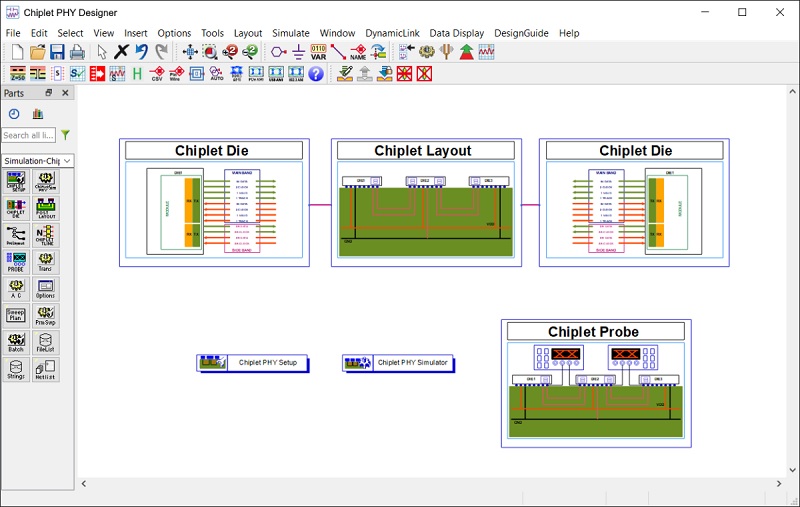

키사이트테크놀로지스가 AI 및 데이터 센터 애플리케이션을 위한 고속 디지털 칩렛 설계 솔루션인 칩렛 PHY 디자이너 2025(Chiplet PHY Designer 2025)를 출시했다.

칩렛 PHY 디자이너 2025는 이번 업그레이드를 통해 UCIe™(Universal Chiplet Interconnect Express™) 2.0 표준에 대한 시뮬레이션 기능이 추가됐으며, 오픈 컴퓨트 프로젝트(Open Compute Project, OPC)와 BoW(Bunch of Wires) 표준도 새롭게 지원한다. 이 소프트웨어는 고급 시스템 수준 칩렛 설계 및 다이-투-다이(D2D) 설계 솔루션으로, 실리콘 생산 전(Pre-Silicon) 검증을 가능하게 하여 테이프아웃 과정을 더 효율적으로 진행할 수 있도록 지원한다.

AI 및 데이터 센터 칩이 점점 더 복잡해짐에 따라 칩렛 간 안정적인 통신이 성능을 결정짓는 중요한 요소가 되고 있다. 이를 해결하기 위해 업계에서는 UCIe 및 BoW와 같은 개방형 표준을 도입하고 있다. 이러한 표준은 2.5D/3D 패키징 및 고급 패키지 기술에서 칩렛 간 인터커넥트 방식을 정의하며, 이를 준수하는 칩렛 설계는 상호 운용성을 높이고 반도체 개발 비용과 리스크를 줄이는 데 기여한다.

칩렛 PHY 디자이너 2025는 UCIe 2.0 및 BoW 표준을 준수하는 설계를 검증할 수 있어, 최신 패키징 생태계에서 칩렛의 원활한 통합이 가능해졌다. 또한, 전압 전달 함수(Voltage Transfer Function, VTF) 등의 자동 시뮬레이션 및 규정 준수 테스트 설정을 지원해 칩렛 설계 워크플로를 단순화하고, 설계 초기 단계에서 정확성을 높일 수 있도록 돕는다. 이뿐 아니라 신호 무결성, 비트 오류율(Bit Error Rate, BER), 크로스톡 분석을 통해 실리콘 재설계(re-spin)의 위험을 줄이고, 고속 인터커넥트의 동기화 강화를 위해 쿼터 레이트 데이터 속도(Quarter-Rate Data Rate, QDR)와 같은 고급 클로킹 기법 분석도 지원한다. 이를 통해 설계자는 더욱 정밀한 클로킹 시스템을 구현할 수 있다.

AEM(오토모티브일렉트로닉스매거진)

<저작권자 © AEM. 무단전재 및 재배포 금지>