2019-05-08 / 05월호 지면기사

/ 글│더그 스미스(Doug Smith) _ 멘토, 지멘스 비즈니스

IT’S NOT MY FAULT! HOW TO RUN A BETTER FAULT CAMPAIGN USING FORMAL

결함 분석, 형식 기법으로 더 우수한 캠페인 실행

시뮬레이션을 이용한 결함 주입은 시간이 오래 걸리고 지루할 수 있으며, 디자인이 테스트를 위해 결함을 전파시키는 방식으로 작동하지 않을 수도 있다. 하지만 형식 검증을 이용하면 최악의 경우의 진단 커버리지를 제공하는 구조적 분석을 통해 결함을 손쉽게 분류할 수 있다. 게다가, 결함을 분석하여 전파, 안전목표 위배 및 결함 감지를 확인함으로써 정확하고 신뢰도 높은 결과를 제공한다. 본고에서는 형식 기법을 이용해 보다 나은 결함 캠페인을 실행하는 방법을 자세히 설명한다.

글│더그 스미스(Doug Smith) _ 멘토, 지멘스 비즈니스

ISO 26262 자동차 안전 표준에서는 무작위적인 하드웨어 결함으로 인한 안전목표 위배를 평가함으로써 안전 지표 계산을 위한 진단 커버리지(DC)를 알아낼 것을 요구한다. 시뮬레이션을 이용한 결함 주입은 시간이 오래 걸리고 지루할 수 있으며, 디자인이 테스트를 위해 결함을 전파시키는 방식으로 작동하지 않을 수도 있다. 하지만 형식 검증을 이용하면 최악의 경우의 진단 커버리지를 제공하는 구조적 분석을 통해 결함을 손쉽게 분류할 수 있다. 게다가, 결함을 분석하여 전파, 안전목표 위배 및 결함 감지를 확인함으로써 정확하고 신뢰도 높은 결과를 제공한다. 본고에서는 형식 기법을 이용해 보다 나은 결함 캠페인을 실행하는 방법을 자세히 설명한다.

두 가지 검증 요건

자동차 기능안전성 표준인 ISO 26262는 자동차 애플리케이션에 사용되는 IC에 대해 검증 요건 두 가지를 정의하고 있다. 체계적인, 시스템적인 고장 검증과 무작위적 하드웨어 고장 검증이 바로 그것이다. 체계적인 고장이란 전형적인 기능 검증에서 발견되는 설계 상의 버그이다. 무작위적 하드웨어 고장 검증에서는 결함을 디자인에 주입하여 해당 디자인의 안전 메커니즘에 대한 가정사항들을 테스트함으로써 이들이 제대로 작동하는 지 살펴본다. 기능 검증에서 커버리지를 이용해 완전성을 알아내듯이, ISO 표준도 무작위적 하드웨어 고장에 대한 커버리지의 한 형태를 정의하고 있다. 이를 진단 커버리지(diagnostic coverage)라고 하며, 안전 메커니즘에 의해 커버되는 안전 요소의 비율을 나타낸다.

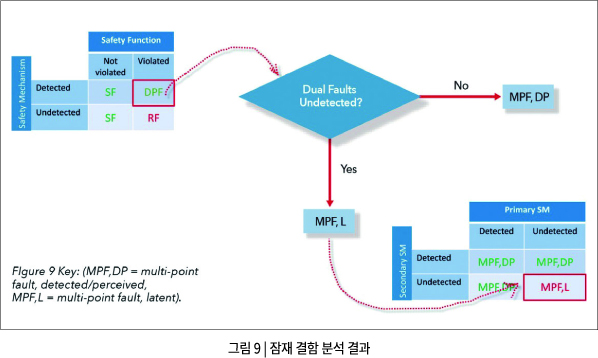

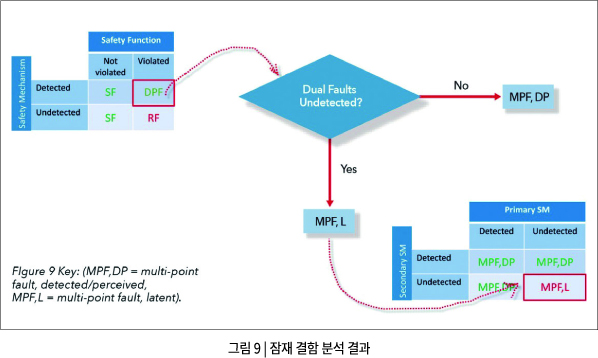

진단 커버리지는 먼저 디자인 내에 존재하는 여러 다른 결함 유형의 수를 알아냄으로써 산출된다. 결함이 주입되었는데도 안전 필수 목표(기능)나 출력에 아무런 영향도 없다면 안전한 것으로 간주된다. 마찬가지로, 주입된 결함을 자동차 운전자가 감지하거나 알림을 받을 수 있다면 이 또한 안전한 것으로 간주된다. 우리가 정말로 알아내고자 하는 것은 어떠한 안전 메커니즘으로도 보호되지 않는 결함(단일 지점 결함으로 알려진)이나, 커버하게 되어 있지만 안전 메커니즘이 이를 감지하지 못하는 결함(잔여 결함이라 부르는)이다. ISO 표준은 안전 메커니즘의 잠재적인 결함들도 다룬다. 전형적으로, 자동차 디자인은 일차 안전 메커니즘의 거동을 점검하기 위해 POST와 같은 이차 안전 메커니즘을 갖는다. 안전 메커니즘이 적절한지 테스트하기 위해서는 결함을 디자인에 주입해 일차 안전 메커니즘을 작동시킨 뒤에, 두 번째 결함을 일차 안전 메커니즘에 주입하여 여전히 제대로 작동하는 지 살펴보아야 한다. 이를 이중 지점 결함이라고 하며, 이는 다중 지점 결함 범주로 분류된다(해당 표준에서는 최대 2개의 결함만 테스트하면 되지만, 아키텍처 상의 이유로 더 많은 결함을 테스트해야 할 경우는 예외이다). 이차 안전 메커니즘에 의해 커버되지 않는 이중 지점 결함은 잠재 결함으로 간주된다.

디자인 내의 모든 결함을 분류하고 나면 ISO 26262 지표를 산출하기가 쉽다. 결함 수를 FMEDA[1]에 한데 모아 단일 지점 결함 지표(SPFM)나 잠재 결함 지표(LFM)를 산출하는 경우가 많다. 또는 진단 커버리지를 백분률로 산출한 뒤에 FMEDA에 특정 고장 모드[3]의 프로세스 FIT[2]율(λFIT)과 조합하여 사용할 수도 있다. (ISO 지표의 산출에 대한 자세한 내용은 섹션 C.1~C.3의 [1] 참조).

안전 요소와 안전 메커니즘

자동차 전장은 항상 블랙박스로 취급되어 왔기 때문에 부품 하나가 고장을 일으키면 다른 부품으로 교체되었다. 따라서 ISO 표준에서 안전 요소와 안전 메커니즘을 언급할 경우, 이는 전통적으로 이산형 부품으로 취급했으므로 무엇이 안전 부품인지 명백했다.

하지만 기술 발전으로 모든 것을 IC 하나에 집어넣을 수 있게 됨에 따라 안전 관련 부품과 비 안전 관련 부품 간의 경계가 모호해지고 있다. 예를 들어, 레지스터는 디자인의 서로 다른 안전 및 비 안전 관련 부품들 간에 공유될 수 있다. 이 때문에 문제가 복잡해진다. 결함 지표의 산출에는 안전 관련 요소만을 사용해야 하는데, 안전/비 안전 로직이 한데 섞임에 따라 디자인 전체가 안전 구성요소가 되기 때문이다. 비 안전 관련 로직의 제거를 정당화할 수 있는 유일한 길은 안전 로직과 비 안전 로직이 서로 독립적임을 보여주는 것인데, 이는 종속 고장 분석(DFA: dependent failure analysis)을 이용해 가능하다. 하지만 독립성을 증명하기란 대개 쉽지 않으며, 모든 설계 로직을 포함시킬 경우 필요 이상의 결함을 주입하게 된다. 이는 진단 커버리지를 약화시킬 가능성이 높다.

IC 내의 안전 요소들을 찾아내는 대신에(로직은 아마도 다수의 모듈에 걸쳐있을 것이므로), 한데 결합되어 안전 목표나 안전 기능을 형성하는 안전 필수 경로들을 찾아내는 편이 더 쉽다. 마찬가지로, 결함은 다수의 안전 메커니즘을 통해 감지할 수도 있으며, 이 중의 어느 것이라도 결함의 감지나 인지에 상당할 수 있다. 따라서 IC에서 안전 요소라는 개념은 모듈의 경계와는 관련성이 적고, 관련 안전 로직(아마도 안전 도메인[4]이라고 부르는 편이 더 정확할 것이다)과의 관련성이 더 크다.

캠페인 트레일

모든 안전 메커니즘이 완전히 기능적으로 검증되었다고 가정하자. 그러면 이제는 무작위적 하드웨어 테스트를 수행할 때이다. 이를 결함 캠페인(fault campaign)이라고도 한다. 상위 안전 개념에 따라서는 각 유형의 고장 모드(대개 0고착결함 모드, 1고착결함 모드 또는 트렌지언트 결함 모드)에 대해 하나씩, 다수의 결함 캠페인을 수행해야 할 수도 있다.

결함 캠페인에는 네 단계가 필요하다. 첫째, 결함을 작동시켜야 한다. RTL 디자인에서는 모든 네트, 레지스터 및 포트가 잠재적 결함이다. 이것만 해도 수많은 결함이지만, 게이트 수준의 넷리스트에는 몇 배나 더 되는(수백만 개의) 결함이 있다. 잠재 결함 분석을 위한 이중 지점 결함까지 고려할 경우, 가능한 결함의 수는 천문학적이 된다. 현실적으로, 시뮬레이션을 통해 모든 결함을 테스트하기에는 시간이 너무 오래 걸린다. 그 대신 잠재 결함을 무작위적으로 샘플링(대개 수천 개)한 뒤, 이를 시뮬레이트하여 통계적으로 허용 가능한 오차범위를 캠페인 결과에 제공한다.

두 번째 단계는 결함을 설계 전반에 전파시키는 것이다. 회귀 테스트를 결함 주입에 사용할 수 있지만, 결함이 실제로 전파되도록 하려면 추가적인 노력을 기울여야 한다. 예를 들어, 설계 로직이 잘못된 상태에 있다면 결함이 전파되지 못할 수도 있다. 이 때문에 약간의 수작업적인 노력과 검사 또는 커버리지 지표의 이용이 요구되거나, 혹은 선택된 테스트가 전혀 쓸모 없을 수도 있다는 사실을 무시해야 한다. 다시 말해, 시뮬레이션 결과는 통계적 표본추출이라는 관점에서는 높은 신뢰성을 제공할 수 있지만, 결과가 실제로 의미 있는 것이라는 확신은 별로 주지 못한다.

세 번째 단계는 결함을 관찰하거나 해당 결함이 제어 또는 감지되었음을 나타내는 것이다. 테스트벤치는 고장을 점검 및 표시하기에는 좋지만, 결함 캠페인에는 방해가 될 수 있다. 무작위적 결함을 주입하면 시뮬레이션이 형편없이 엇나가서 결함이 감지 가능할 정도로 전파되기도 전에 실패하고 말 수도 있다. 테스트를 황금의 시뮬레이션 파형(즉, 결함이 주입되지 않은 시뮬레이션 파형)과 비교하여 그 안전 출력들이 서로 다르면 고장으로 간주하는 경우도 많다. 유감스럽게도, 여기서는 출력이 다를 경우 결함을 뜻하는 것으로 가정하고 있다. 결함을 주입하면 디자인이 합법적인 다른 경로로 빠지고 말 수도 있다. 마찬가지로, 안전 기능과 메커니즘이 파형에서는 서로 달라도 안전 메커니즘이 실제로 고장을 감지할 수도 있다. 테스트는 실제로는 성공적인 것으로 간주되어야 하는데도 실패로 표시될 수도 있다. 반대로, 테스트에서는 어떠한 결함도 확인되지 않아 합격이라는 결과를 얻었지만, 결함이 감지되지 않은 것이므로 해당 테스트는 실패로 간주되어야 할 수도 있다. 따라서 결과를 해석해야 하며, 결함감지간격(FDI: fault detection interval)도 고려해야 한다. 고장감지간격은 결함이 전파되다가 감지되어 안전하지 못한 것으로 간주되기까지 걸리는 최대 시간을 명시한다.

마지막으로, 네 번째 단계는 결과를 보고하는 것이다. 자원 공유가 이루어지는 IC에서 결함 주입의 결과를 병합시켜야 한다. 예를 들어, 안전 기능이 그림 1과 같이 디자인을 통과하는 다수의 안전 필수 경로들로 구성되어 있다고 가정하자. 이 결함은 경로 1에 아무런 영향도 미치지 않는다. 따라서 이 결함은 안전하다는 뜻이 된다. 하지만 경로 2에서는 결함이 안전 메커니즘에 감지되지 않고 지나간다. 따라서 이것은 잔류결함이다. 이 예에서 경로 2의 잔류 결함은 경로 1의 안전한 결과보다 우선순위가 높으므로 병합된 결과는 잔류 결함으로 간주된다. 결함의 우선순위는 ISO 표준[2] 파트 5의 플로우차트 B.2로부터 추론할 수 있다.

.jpg) 보다 스마트한 작업 방식

보다 스마트한 작업 방식

보다 스마트한 작업 방식에 해당되는 것이 바로 형식 분석이다. 형식 분석에서는 분석 작업을 수행하기 위해 디자인을 부울 표현으로 합성해야 한다. 디자인의 규모는 상관 없으며, 그 디자인이 합성 가능한지만이 중요하다. 덕분에 형식 툴은 신호의 영향권, 즉, 신호에 영향을 미칠 가능성이 있는 모든 로직을 역추적할 수 있다. 무작위적 하드웨어 고장 분석이라는 맥락에서 영향권(COI)은 추가 분석 없이도 구조적으로 안전한 모든 결함들을 자동적으로 제거할 수 있다. 아래의

그림 2에서 보듯이, 영향권 밖에 있는 모든 것은 정의상 안전한 결함으로 분류되기 때문이다. 뿐만 아니라, 영향권은 어떤 로직이 안전 메커니즘에 의해 커버되는지 여부를 밝혀줄 수 있어, 단일 지점 결함, 잔여 결함 및 잠재 결함을 보여준다. 이 구조적 분석은 결함 주입이 수행되기 전에 신속한 분류를 제공한다. 이는 진단 커버리지의 계산을 위한 최악 또는 최상의 시나리오를 제공한다.

결함이 디자인 전체로 전파되기 위해 필요한 최소한의 사이클 수를 살펴봄으로써 구조적 결함을 추가로 제거할 수 있다. 전파 시간이 하드웨어 요건에서 명시하는 결함감지간격이나 다중 지점 결함감지간격보다 길 경우에는 정의상 감지할 수 없으며, 더 이상의 분석 없이 분류할 수 있다. 디자인을 제한함으로써 추가로 결함을 제거할 수 있다. 이로 인해 형식 합성이 마치 합성 툴처럼 로직을 제거하게 된다. 마지막으로, 적절한 형식 엔진이 주어진다면 ATPG 알고리즘처럼 결함이 구조적으로 동등하거나 우세함을 입증할 수 있을 경우 이를 압축할 수 있다.

.jpg)

구조적 분석은 일반적으로 매우 신속하며, 아래의

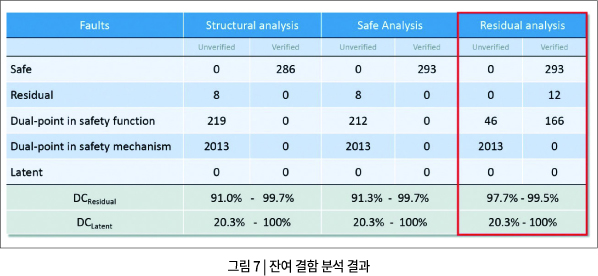

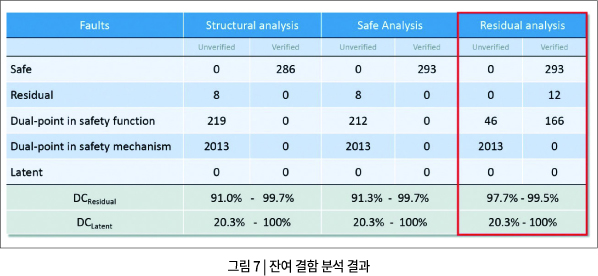

그림 3에서 보듯이 최악의 경우/최상의 경우의 진단 커버리지를 산출한다. 이 예제에서는 이 RTL 모듈의 영향권 밖에 286 상태 비트가 있으므로 이들은 자동적으로 안전한 것으로 분류된다. 다른 상태 비트는 잔여 결함이나 이중 지점 결함으로 분류되지만, 추가적인 분석 없이는 검증되지 않는다. 이들이 검증되지 않은 것으로 표시되는 이유는 구조적으로는 특정 유형의 결함처럼 보일지 몰라도 일단 결함이 주입되었을 때 안전 목표에 영향을 미치거나 감지되리라는 보장이 없기 때문이다. 이러한 결함들을 검증된 범주로 옮기기 위해서는 형식 분석을 수행해야 한다. 안전 기능 내의 모든 이중 지점 결함이 잔여 결함이라는 최악의 시나리오를 가정하면 최악의 경우의 잔류 진단 커버리지를 산출할 수 있다. 마찬가지로, 안전 메커니즘 내의 모든 이중 지점 결함이 잠재 결함이라고 가정하면 최악의 경우의 잠재 진단 커버리지를 산출할 수 있다. 이는 안전 ASIL 목표가 ASIL-B(90%)일 뿐이라면 잔여 결함에 대해 더 이상의 분석은 필요 없다는 뜻이다. 구조적으로 커버리지는 91% 이하가 될 수 없기 때문이다. 반면에 20%의 잠재 진단 커버리지는 ASIL-B 수준(60%) 미만이므로 잠재 결함 분석이 필요하다.

결함 분석

형식 기법의 구조적 분석을 이용하면 결함 캠페인의 첫 번째 주요 해결과제인 작동시켜야 하는 결함 수를 줄이는 데 큰 도움이 된다. 두 번째 주요 해결과제는 결함을 설계 전반에 전파시키는 것이다. 앞서 언급했듯이, 결함이 디자인 전반에 실제로 전파됨을 시뮬레이션에서 입증한다는 것은 사소한 문제가 아니다. 하지만 형식 기법에서는 결함의 전파가 보장된다. 형식 기법은 상태 공간 전반을 철저하게 가로지름으로써 임의의 결함이 전파될 수 있는 지 여부를 입증하거나 반증하기 위해 가능한 모든 경로를 찾아낸다. 결함이 해당 경로를 안전 기능이나 안전 메커니즘에 민감해지도록 하기 위해 어떠한 수작업 검사나 수작업에 의한 테스트 작성 또는 커버그룹 작성도 필요하지 않다. 더욱 좋은 점은, 형식 기법에는 스티뮬러스 제공이 필요 없으며 테스트벤치도 필요 없다는 점이다. 형식 툴은 스티뮬러스를 자동적으로 결정한다. 전통적인 형식 검증에서 형식 기법은 불법적인 상태나 정의되지 않은 상태를 포함한 모든 경로를 철저하게 따라가므로 미탐(false negatives)이 야기된다. 하지만 결함 전파를 위해 SLEC(Sequence Logic Equivalency Checking)라고 하는 전문적인 형식 앱을 사용할 수 있다.

SLEC을 이용해 두 디자인이 동등함을 입증할 수 있다. 하지만 레지스터들 간의 조합 로직이 동등하다는 것만 확인하는 LEC(logic equivalency checking)와는 달리, SLEC는 두 디자인의 기능 출력이 동등함을 확인한다. 다시 말해, 디자인은 출력만 동등하다면 상이한 내부 시간으로 전혀 다르게 구현할 수 있는 것이다. SLEC는 입력들을 자동적으로 한데 묶어 스티뮬러스를 적용한 뒤 출력들이 동일한지 확인한다. SLEC는 디자인이 VHDL로부터 Verilog로 올바르게 이식되었는지 또는 디자인에 여분의 로직을 추가할 경우 디자인이 주된 기능(치킨 비트의 사용과 같은)에 영향을 미치지 않는지 확인하는 것과 같은 많은 용도를 갖고 있다.

결함 캠페인에서 SLEC은 사용자 입력 없이도 입력을 제한할 수 있는 메커니즘을 제공한다. 시험 대상 디자인(DUT)은 그 자신과 비교되며, 결함이 이 DUT의 다른 인스턴스에 주입된다. 결함으로 인해 출력이 달라지지 않는다면(즉, 두 인스턴스가 결함이 주입되어도 동등하다면) 이 결함은 안전 목표를 위배할 수 없으며 안전한 것으로 입증된다. 입력들은 한데 묶여 있으므로 형식 입력은 원래의 디자인에 의해 제한된다. 즉, 이 디자인을 통과하는 합법적인 값들만이 오류가 주입된 인스턴스를 통해 보내질 수 있다. 따라서 수작업으로 작성된 테스트나 제약사항이 필요 없으며, 상태 공간을 철저하게 탐색할 수 있다.

형식 기법을 이용해 결함을 주입하려면 조건부 차단점을 생성해야 한다. 차단점은 드라이버를 제거하여 형식 제어점이 된 네트나 레지스터로서, 이를 이용해 고착 결함이나 트렌지언트 결함을 생성할 수 있다. SLEC를 통해 커버 속성도 사용할 수 있으므로, 특정 결함이 주입될 경우 안전 목표 위배가 발생하며 이는 지정된 시간 간격 내에서 감지될 것임을 명시할 수 있다.

.jpg)

형식 SLEC를 이용한 결함 분석은 (1) 안전 결함 분석, (2) 잔여 결함 분석 및 (3) 잠재 결함 분석의 세 단계로 나눌 수 있다. 안전 결함 분석에서는 결함을 주입하여 이것이 제약 없이 디자인 전체로 전파되는지 확인해보게 된다. 출력이 동등하게 유지된다면 결함은 안전한 것으로 입증된다. 이것은 형식 기법에 있어서 보다 손쉬운 증거이다. 잔여 결함 분석은 지정된 시간 간격 내에서 감지되지 않는 안전 목표 위배를 확인해야 하기 때문이다. 제약 없는 SLEC는 대개 매우 빠르지만, 영향권 내의 결함은 대부분 안전 입력에 아무런 영향도 미치지 않을 가능성이 별로 없다.

그림 5에서 보듯이 안전 결함은 증가하는데, 이는 안전 기능 내의 이중 지점 결함 중 일부가 안전한 것으로 입증되었기 때문이다.

.jpg)

그 다음으로, 잔여 결함 분석이 SLEC를 이용해 수행되는데, 이는 안전 기능 내의 모든 이중 지점 결함을 감지할 수 있는 지 알아내기 위해서이다

(그림 6). 감지될 수 없는 것은 안전 메커니즘이 커버하지 못하는 것이므로 잔여 결함이다.

그림 7은 결함이 검증됨에 따라 그 일부는 잔류 또는 감지 가능한 결함임이 입증될 수 있음을 보여준다. 이는 잔류 진단 커버리지의 범위를 좁혀준다.

.jpg)

이중의 문제

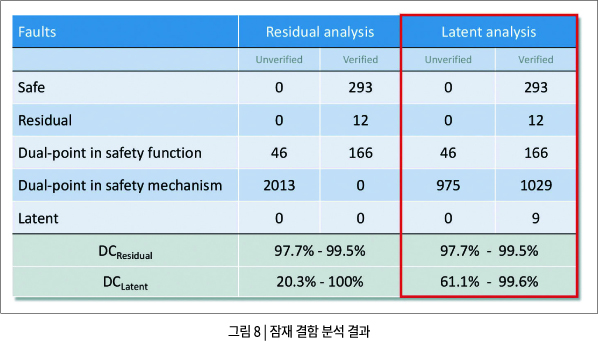

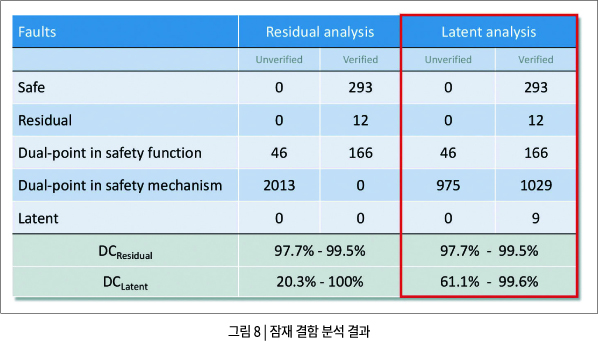

그림 8은 안전 메커니즘 내의 이중 지점 결함이 감지 가능한 것으로 확인됨에 따라 잠재 진단 커버리지 범위가 보다 수용 가능한 수준으로 좁아짐을 보여준다.

형식 기법의 우수성

형식 기법의 우수성

물론 형식 기법에도 한계는 있다. 합성 가능한 디자인이 필요한데, 이는 일부 구성요소들이 블랙박스일 수 있음을 뜻한다. 상태 공간과 메모리가 가장 큰 한계이므로 문제의 분해와 같은 전형적인 형식 기법을 사용해야 할 수도 있다. 마찬가지로, 보다 작은 블록들에서 실행하여 그 결과들을 하나의 보다 큰 FMEDA로 합치는 편이 보다 실용적일 수 있다. 형식 기법에서 합쳐지지 않는 결함들은 시뮬레이션이나 에뮬레이션(형식 기법은 특정 활동을 겨냥한 시뮬레이션 테스트벤치까지도 생성할 수 있다)으로 내보내 정상적인 회귀 방식으로 실행할 수 있다.

진단 커버리지 범위를 결함 캠페인 초기에 즉각 생성할 수 있는 기능은 형식 기반 흐름을 사용할 경우의 최대 이점 중 하나이다. 형식 기법은 다른 결함 캠페인 문제들에 대해서도 보다 나은 솔루션을 제공한다.

이는 분석에 필요한 결함 수를 크게 줄일 수 있다. 그 결과는 입증된 것으로서 철저하지만, 이는 시뮬레이션이나 에뮬레이션 흐름에서는 실용적이지 못하다. 결함은 작동, 전파 및 관찰이 보장된다. 노동집약적 수작업에 의한 테스트 및 테스트벤치는 필요 없으며, 형식 흐름 전체를 안전 기능 신호와 안전 메커니즘을 기술하는 단지 몇 개의 입력만을 기반으로 자동화할 수 있다. 마지막으로, 형식 기법을 이용하면 이중 지점 결함이나 심지어는 무작위적인 트렌지언트 결함도 간단하게 추가할 수 있는데, 이는 형식 기법이 모든 입력을 다루기 때문이다. 형식 기법이 기능 안전 결함 캠페인의 실행을 위한 보다 우수한 방법인 것은 바로 이 때문이다.

참고 문헌

[1] ISO 26262:5-2011. Road vehicles - Functional Safety - Part 5: Product development at the hardware level. International Standardization Organization.

[2] ISO 26262:5-2018. Road vehicles - Functional Safety - Part 5: Product development at the hardware level. International Standardization Organization.

[3] Doug Smith. How Formal Reduces Fault Analysis for ISO 26262. White Paper.

[4] Avidan Efody. Picking Your Faults: Advanced Techniques for Optimizing ISO 26262 Fault Analysis. White Paper.

주

[1] FMEDA = Failure Mode Effects and Diagnostic Analysis(고장 모드의 영향 및 진단 분석). 대개 스프레드시트 형태이다.

[2] FIT = Failure In Time(10억 시간당 고장발생 횟수).

[3] 전형적인 고장 모드는 0 고착결함(stuck-at 0), 1 고착결함(stuck-at 1) 및 트렌지언트 결함(transient faults)이다.

[4] 안전 도메인(safety domain)은 ISO 26262 용어가 아니지만, 여기서는 관련된 모든 안전 필수 로직을 나타내기 위해 사용되었다.

AEM(오토모티브일렉트로닉스매거진)

<저작권자 © AEM. 무단전재 및 재배포 금지>

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)