저전력 FPGA 솔루션 기업인 래티스 반도체(Lattice Semiconductor Corporation)가 12월 10일(미국 시간) 하나의 FPGA 플랫폼에서 다양한 제품을 개발하는 플랫폼 비즈니스 전략과 함께 삼성의 28 nm FD-SOI 공정으로 제조되는 '래티스 넥서스(Lattice 'Nexus)' 플랫폼을 발표했다. 또한 28 nm FD-SOI 공정의 1세대 제품 'CrossLink-NX'도 발표했다.

래티스 넥서스 플랫폼은 1) 설계 재사용 극대화, 2) 개발 비용 저감 3) 비트 레이트(beat rate) 가속화에 초점을 맞쳤다. CrossLink-NX는 백 바이어스 전압을 선택적으로 변경해, 적용하는 애플리케이션 요구에 따라 디바이스당 성능과 전력의 최적화가 가능하다는 점이 눈에 띈다. 구체적으로 타사 28 nm 공정 제품 대비 75%의 정적 파워((static power) 절감이 가능하다고 한다.

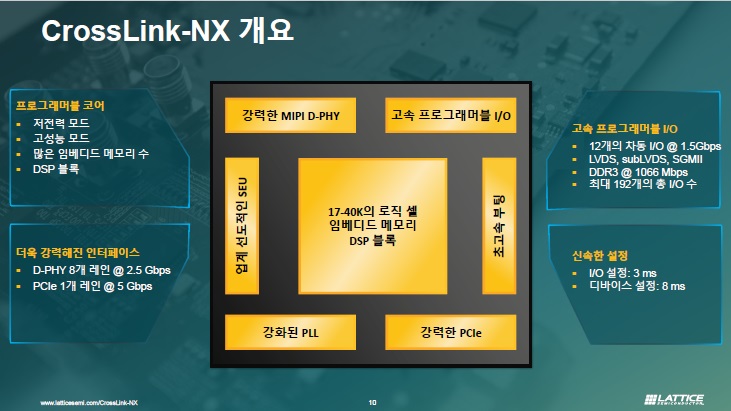

CrossLink-NX는 로직 셀 당 170비트의 임베디드 메모리를 지원함으로써 엣지 디바이스에서 효율적인 AI 추론이 가능하다. 불과 3 ms만에 I/O 설정이 가능하고 전체 디바이스 설정도 15 ms 이내에 가능하다. 따라서 시스템 부팅 시간이 길면 안 되는 산업용 모터 제어나 또는 반응형 임베디드 디스플레이, 보안성이 중요한 앱과 같은 애플리케이션을 보다 효과적으로 지원한다. 또한 FD-SOI 도입으로 소프트 에러를 일으킬 수 있는 영역을 줄임으로써 소프트 에러율(Soft Error Rate, SER)을 벌크 실리콘 기반의 경쟁사 FPGA 대비 1/100로 낮췄다.

.jpg) 래티스 반도체의 잉 젠 첸(Ying Jen Chen, 사진) 아태지역 사업개발 디렉터에 따르면, 40K 로직 셀의 CrossLink-NX는 소프트 에러율이 21.84 FIT(Failures-in-Time)인데 비해 52K 로직 셀의 경쟁사 FPGA는 3102.12 FIT이다. MTBF(Mean Time Between Failure)는 각각 5,359년, 38년이다. CrossLink-NX는 4 입력 LUT(Look-Up Table)를 사용해 배선 영역의 절감 등을 통해 40K 로직 셀 단위로 칩 크기를 6mm × 6mm를 실현했다. 또한 프로그래밍 가능한 I/O도 최대 192개, 2.5 Gbps의 MIPI D-PHY와 같은 기능 확대를 실현했다.

래티스 반도체의 잉 젠 첸(Ying Jen Chen, 사진) 아태지역 사업개발 디렉터에 따르면, 40K 로직 셀의 CrossLink-NX는 소프트 에러율이 21.84 FIT(Failures-in-Time)인데 비해 52K 로직 셀의 경쟁사 FPGA는 3102.12 FIT이다. MTBF(Mean Time Between Failure)는 각각 5,359년, 38년이다. CrossLink-NX는 4 입력 LUT(Look-Up Table)를 사용해 배선 영역의 절감 등을 통해 40K 로직 셀 단위로 칩 크기를 6mm × 6mm를 실현했다. 또한 프로그래밍 가능한 I/O도 최대 192개, 2.5 Gbps의 MIPI D-PHY와 같은 기능 확대를 실현했다.

래티스 반도체에 따르면, CrossLink-NX는 산업 및 자동차 분야 사용자들이 서로 다른 비디오 브릿징, 애그리게이션, 스플리팅 애플리케이션을 단 한 개의 소자를 사용해 쉽고 빠르게 개발할 수 있게 함으로써 개발시간과 자원을 대폭 줄여준다.

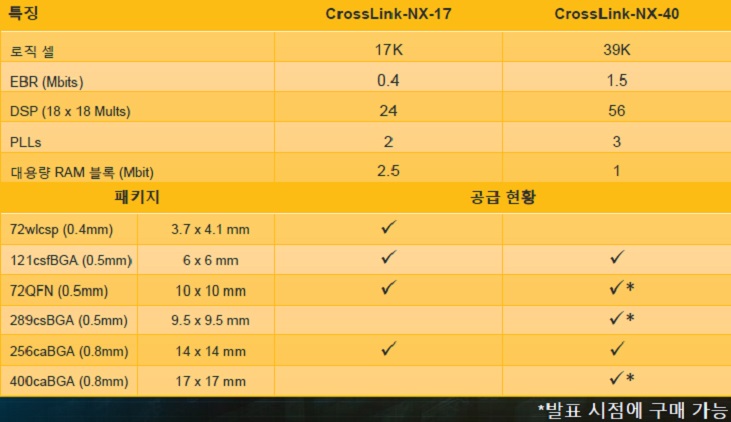

CrossLink-NX 제품군은 로직 셀이 17K(CrossLink-NX-17)와 40K(CrossLink-NX-40)인 두 가지 제품으로 제공된다. 기본적으로 40K 제품이 DSP와 PLL 수는 많지만, RAM 블록의 경우는 40K 제품이 1 Mbit, 17K 제품이 2.5 Mbit이다.

AEM(오토모티브일렉트로닉스매거진)

<저작권자 © AEM. 무단전재 및 재배포 금지>